为高电平且在向低电平改变的期间,以及传输完毕时 CS 为低电平且在向高电平改变的期间。CPHA 为挑选时钟相位。

依据CPHA位的状况,运用时钟上升沿或下降沿来采样和/或移位数据。主机有必要依据从机的要求挑选时钟极性和时钟相位。依据 CPOL 和 CPHA

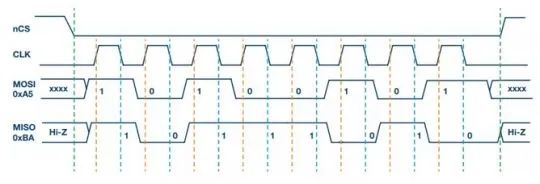

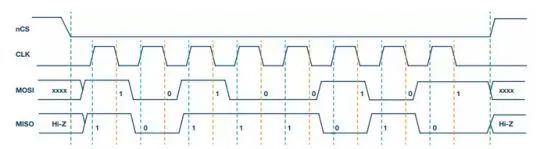

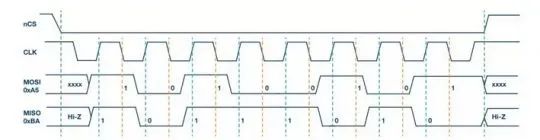

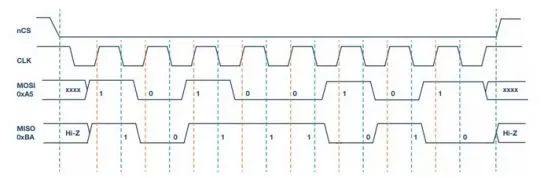

图2至图5显现了四种SPI形式下的通讯示例。在这些示例中,多个方面数据显现在MOSI和MISO线上。传输的开端和完毕用绿色虚线表明,采样边沿袭橙色虚线表明,移位边沿袭蓝色虚线表明。请注意,这些图形仅供参阅。要成功进行SPI通讯,用户须参看产品数据手册并保证满意器材的时序标准。

图2给出了SPI形式0的时序图。在此形式下,时钟极性为0,表明时钟信号的闲暇状况为低电平。此形式下的时钟相位为0,表明数据在上升沿采样(由橙色虚线显现),而且数据在时钟信号的下降沿移出(由蓝色虚线:CLK闲暇状况 = 低电平,数据在上升沿采样,并在下降沿移出

图3给出了SPI形式1的时序图。在此形式下,时钟极性为0,表明时钟信号的闲暇状况为低电平。此形式下的时钟相位为1,表明数据在下降沿采样(由橙色虚线显现),而且数据在时钟信号的上升沿移出(由蓝色虚线:CLK闲暇状况 = 低电平,数据在下降沿采样,并在上升沿移出

图4. SPI形式2,CPOL = 1,CPHA = 1:CLK闲暇状况 = 高电平,数据在下降沿采样,并在上升沿移出

图4给出了SPI形式2的时序图。在此形式下,时钟极性为1,表明时钟信号的闲暇状况为高电平。此形式下的时钟相位为1,表明数据在下降沿采样(由橙色虚线显现),而且数据在时钟信号的上升沿移出(由蓝色虚线:CLK闲暇状况 = 高电平,数据在上升沿采样,并在下降沿移出

声明:本文内容及配图由入驻作者编撰或许入驻协作网站授权转载。文章观念仅代表作者自己,不代表电子发烧友网态度。文章及其配图仅供工程师学习之用,如有内容侵权或许其他违规问题,请联络本站处理。告发投诉

按位传输,高位在前,低位在后,为全双工通讯,数据传输速度整体来说比 I2C 总线要快,速度可到达 Mbps 等级。依据

_SCKMODE寄存器来装备;在QSPI1和QSPI2中没找到相关寄存器,怎么装备QSPI1和QS

噪声讨论材料下载的电子材料下载,更有其他相关的电路图、源代码、课件教程、中文材料、英文材料、参阅规划、用户攻略、解决方案等材料,期望有时机可以协助到广阔的电子工程师们。

噪声讨论材料下载 /

噪声丈量解析材料下载的电子材料下载,更有其他相关的电路图、源代码、课件教程、中文材料、英文材料、参阅规划、用户攻略、解决方案等材料,期望可以在必定程度上协助到广阔的电子工程师们。

噪声丈量解析材料下载 /

串行外围设备接口是由 Motorola 公司开发的,用来在微控制器和外围设备芯片之间供给一个低成本、易运用的接口。这种接口可拿来衔接存储器、AD/DA转换器、实时

有四个作业形式 /

与微控制器的接口 /

)的4种组合决议的。CPOL决议总线闲暇时,SCK是高电平仍是低电平(CPOL=,0,无数据传输时,SCK=0;CPOL

作业形式有几种 /

通讯协议介绍 /

PGA411-Q1 Step-by-Step Initialization With Any Host System