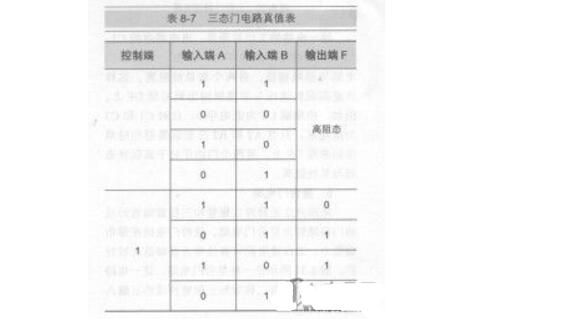

三态门(Three-state gate)是一种重要的总线接口电路。三态门都有一个EN控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态器件。当EN有效时,三态电路呈现正常的“0”或“1”的输出;当EN无效时,三态电路给出高阻态输出。

如果你的设备端口要挂在一个总线上,一定要通过三态缓冲器。因为在一个总线上同时只能有一个端口作输出,这时其他端口必须在高阻态,同时能输入这个输出端口的数据。所以你还需要有总线控制管理,访问到哪个端口,那个端口的三态缓冲器才可以转入输出状态。这是典型的三态门应用。

三态门有三种输出状态:输出高电平、输出低电平和高阻状态,前两种状态为工作状态,后一种状态为禁止状态。有必要注意一下的是,三态门不是具有三种逻辑值。在工作状态下,三态门的输出可为逻辑‘0’或者逻辑‘1’;在禁止状态下,其输出呈现高阻态,相当于开路。

三态门有广泛的应用,利用三态门能轻松实现线与,也被大范围的应用于总线传送。总线传送时,为了能够更好的保证数据传送的准确性,任意时刻,n个三态门的控制端只能有一个为1,其余均为0,而三态门利用高阻态可以很好的实现这一特性。

上图为三态门输出门电路的原理图。在图中,如果将虚线方框内的两个反相器和一个二极管剪掉,剩下的部分就是典型的TTL与非门电路。

所谓三态是指输出端而言。普通的TTL与非门其输出极的两个晶体管T4、T5从始至终保持一个导通,另一个截止的推拉状态。T4导通,T5截止,输出高电平Y=1;T4截止,T5导通,输出低电平,Y=0。三态门除了上述两种状态外,又出现了T4、T5同时截止的第三种状态。因为晶体管截止时c、e之间是无穷大阻抗,输出端Y对地、对电源(vcc)阻抗无穷大。因此这第三种状态也称高阻状态。

三态门电路的图形符EPM3064ATC44-10N号与线所示是三态门电路图形符号。三态门电路控制端对门电路控制状态有两种情况:一是控制端为高电平1时,门电路进入高阻状态,此时的三态门电路的图形符号如图8-29(a)所示,控制端C上有一个小圆圈,二是控制端为低电平0时,门电路进入高阻状态,此时三态门电路的图形符号如图8-29(b)所示,这时的三态门电路图形符号中控制端C上没有小圆圈;就是前面介绍的三态门电路。

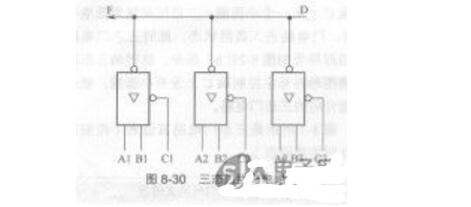

4)三态门线所示是采用三态门构成的线与电路,电路中的DF是数据总线个三态门电路共用的数据传输线,该线与电路要实现这样一个功能,即当其中一个三态门通过总线传输数据时,要求其他两个三态门处于关闭状态。电路中的三态门电路在控制端C接高电平时处于高阻状态。

这一电路的工作原理是:当电路中的Cl、C2和C3轮流为低电平时,总有一个三态门电路与总线相连,另两个与总线脱离,这样就能实现轮流按与非逻辑输出到总线DF上。例如,控制端C2为低电平0,此时Cl和C3为高电平,只有A2和B2与非运算后的结果加到总线DF上,另两个门由于处于高阻状态而与总线脱离。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

输出缓冲器是一种电子元件,其最大的作用是将一个输入信号转换成一个能控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(

中,当EN=1时,对原电路无影响,电路的输出符合原来电路的所有逻辑关系,即A可以输出到B。当EN= 0时,电路内部的所有输出与外部将处于一种关断状态。

的工作原理: 当控制端a为“1”时,b型管3导通,同时a端电平通过反向器成为低电平,让

资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望有机会能够帮助到广大的电子工程师们。

总线电路工作过程波形仿真分析,用环形计数器做实验中的信号源产生所需的各个控制信号、用脉冲信号源产生各数据输入信号,用逻辑分析仪多踪同步显示各个

原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料主要内容有了:1 ModelSimSE的使用流程,2 一个Verilog计数器仿线

主要是用于总线的连接,因为总线只允许同时只有一个使用者。通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。如器件没有选通的话它就处于高阻

指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又能保持特有的高阻抗状态,那么

输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又能保持特有的高阻抗状态。高阻

指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又能保持特有的高阻抗状态。本文开始介绍了

在数字电路上能够说是应用的十分普遍,特别是一些总线上的应用,因而,随着数字电路的发展,就避免不了用硬件描述语言在FPGA上来设计实现

分时轮流工作时的波形进行了仿真实验测试,给出了仿真实验方案,即用Multisim仿线

工作波形的仿真实验技术,即用Multisim仿真软件中的字组产生器产生

电路模块的VHDL程序,这个程序会出现编译不能通过的问题。然后从这样的一个问题出发,通过尝试

:计算机的逻辑部件 常用的集成门电路器件分为两大类:CMOS和TTL。 CMOS是由单极型场效应

虽然能轻松实现线与的功能,但外接电阻Rp的选择要受到一定的限制而不能取得太小,因此影响了工作速度。